PRESIDENCY UNIVERSITY

# Mid - Term Examinations - November 2024

Semester: V Date: 04/11/2024 Course Code: ECE3008 Time: 09.30am to 11.00am Course Name: VLSI Design Max Marks: 50 Program: B.Tech Weightage: 25%

## **Instructions:**

(i) Read all questions carefully and answer accordingly.

(ii) Do not write anything on the question paper other than roll number.

Part A

| Answer ALL the Questions. Each question carries 2marks. |                                                                                                                                                                                |         | 5QX2M=10M |       |  |

|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------|-------|--|

| 1                                                       | What's the relationship between the drain and current in the MOSFET as a function of gate-to-source voltage and drain to source voltage?                                       | 2 Marks | L1        | C01   |  |

| 2                                                       | Define MOS diode and mention at least two applications.                                                                                                                        | 2 Marks | L1        | C01   |  |

| 3                                                       | Define Substrate Bias effect.                                                                                                                                                  | 2 Marks | L1        | CO2   |  |

| 4                                                       | The current conduction in the channel is in the form of drift. If the mobility falls at high temperatures, what can we say about the on-resistance as the temperature goes up? | 2 Marks | L1        | CO2   |  |

| 5                                                       | Identify the region of operation of transistor M1 and M2                                                                                                                       | 2 Marks | L1        | CO1,2 |  |

|                                                         | <u></u>                                                                                                                                                                        |         |           |       |  |

Answer ALL Questions. Each question carries 10 marks.

### Part B

#### MOS transistor switches ON when a proper voltage is applied at 6 6 Marks C01 a. L3 the gate terminal. Calculate the current flow in the NMOS with

## 4QX10M=40M

$2.5V \longrightarrow M_2$   $2V \longrightarrow M_1$

|    |    | the following parameters. L= 2µm. W =10 µm, µ <sub>n</sub> = $0.05m^2/v$ -s, Cox = $1.5 * 10^{-4}$ F/m2, VT = $0.4$ V.                                                                                                                                       |          |    |     |

|----|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----|-----|

|    |    | i). VGS = $0.45v$ , VDS = $0V$                                                                                                                                                                                                                               |          |    |     |

|    |    | ii). VGS = 0.8 v, VDS = 0.4 V                                                                                                                                                                                                                                |          |    |     |

|    | b. | Identify the region of operation for each case.                                                                                                                                                                                                              | 4 Marks  | L1 | C01 |

|    |    | or                                                                                                                                                                                                                                                           |          |    |     |

| 7  |    | The active load is used in n-MOSFET inverter to reduce the area<br>of the chip. Derive small signal gain and output resistance of n-<br>MOSFET inverter with active load.                                                                                    | 10 Marks | L3 | C01 |

| 8  | a. | The metal oxide semiconductor transistor or MOS transistor is a<br>basic building block in logic chips, processors & modern digital<br>memories. Explain the operation for NMOS transistor in<br>different regions (Cut-off, Linear and Saturation regions). | 6 Marks  | L2 | C01 |

|    | b. | Plot the ID-VDS and ID-VGS characteristics for different values of VGS and VDS respectively.                                                                                                                                                                 | 4 Marks  | L2 | C01 |

|    |    | or                                                                                                                                                                                                                                                           |          |    |     |

|    | a. | NMOS transistors operate by creating an inversion layer in a p-<br>type transistor body. Define channel length modulation?                                                                                                                                   | 3 Marks  | L1 | C01 |

| 9  | b. | The current flowing through an NMOS (n-channel metal-oxide-<br>semiconductor) transistor can be described by the basic<br>equation. Derive drain current equation assuming channel<br>length modulation.                                                     | 7 Marks  | L3 | C01 |

| 10 | a. | Discuss small signal equivalent circuit model of MOSFET without considering the effect of channel length modulation modelled by output resistance.                                                                                                           | 5 Marks  | L2 | C02 |

|    | b. | Summarize important Design techniques you would follow when doing a Layout for Digital Circuits?                                                                                                                                                             | 5 Marks  | L2 | CO2 |

|    |    | or                                                                                                                                                                                                                                                           |          |    |     |

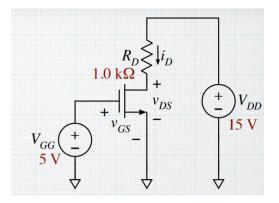

| 11 | a. | NMOS is like a regular switch - applying a voltage (like flipping<br>the switch) turns it on, allowing current (like light) to flow. For<br>the circuit shown, use the the NMOS equations to find ID and<br>VDS.                                             | 7 Marks  | L3 | CO2 |

- **b.** Why is the substrate in NMOS connected to Ground and in PMOS 3 Marks L2 CO2 to VDD?

- a. Stick diagrams are a means of capturing topography and layer 6 Marks L2 CO2 information using simple diagrams. Draw the transistor level schematic (CMOS) and stick diagram for 3 input NAND gate

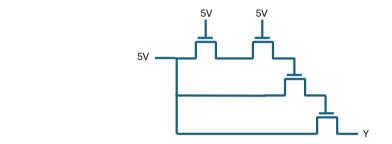

- **b.** For the given circuit, if the threshold voltage of each transistor is 4 Marks L2 CO2 0.5V, then what is the output voltage at node Y.

or

- a. Stick diagrams are used to represent VLSI layouts in an abstract 6 Marks L2 CO2 way, showing the relative placements and connections between different layers like polysilicon, diffusion, and metal layers. Draw the transistor level schematic (CMOS) and stick diagram for 3 input NOR gate

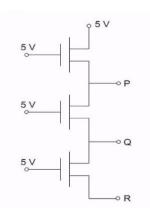

- **b.** Find out the voltage at P, Q, R for given NMOS transistor. Assume 4 Marks L2 CO2 Vt=1V.

13

12