### ROLL NO.

# PRESIDENCY UNIVERSITY, BENGALURU SCHOOL OF ENGINEERING

Max Marks: 80 Max Time: 120 Mins Weightage: 40 %

### **ENDTERM FINAL EXAMINATION**

I Semester AY 2017-18 Course: **CSE 202 DIGITAL DESIGN** 19 DECEMBER 2017

#### **Instructions:**

i. Write legibly

ii. Scientific and non-programmable calculators are permitted

\_\_\_\_\_

#### Part A

[4 Q x 10 M = 40 Marks]

- 1. Enumerate the design steps in combination logic, and design a circuit with three inputs x, y, z and outputs A, B and C. When the binary inputs is 4,5,6 or 7 the binary output is two less than the input and when the input binary input is 0,1,2,or 3 the binary output is one greater than the input.

- 2. Enlist the steps in analysis process of combinational logic and describe with suitable example.

- 3. What is multiplexer? Simplify the Boolean function using 8:1 multiplexer  $f(abcd) = \sum m (1,3,4,11,12,13,14,15)$  and write the logic diagram.

- **4.** What is the difference between flip flop and latch? Write characteristic table and excitation table for SR, JK, D and T flip flop

#### Part B

$[2 Q \times 8 M = 16 Marks]$

- **5.** Design 32:1 multiplexer using only using 8:1 multiplexer and one 4:1 multiplexer.

- **6.** What is demultiplexer? Design using decoder and external gates  $F1(abc) = \sum m(2,4,6,7)$  and  $F2(abc) = \sum m(1,3,5,7)$

- 7. Design a sequential logic using JK flip flop with the following transition when x=1,  $11\rightarrow00\rightarrow10\rightarrow01\rightarrow11$ , and the sequential logic will remain in same state when x=0. Assume state 11 as initial state and 01 as final state. Output is 1 at final state and 0 at all other states.

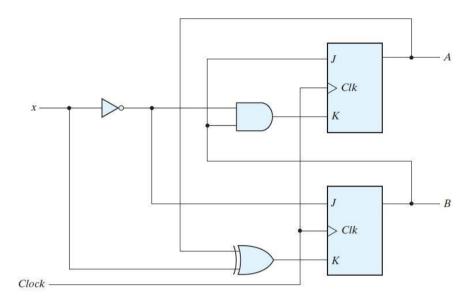

- 8. Analyze the clocked synchronous sequential logic give below

# PRESIDENCY UNIVERSITY, BENGALURU SCHOOL OF ENGINEERING

15M

Max Marks: 40 Max Time: 60 Mins Weightage: 20 % TEST 2 I Semester AY 2017-2018 Course: CSE 202 Digital Design 26 OCT 2017 **Instructions:** i. Write legibly Scientific and non programmable calculators are permitted ii. Part A 1. Define the terms Prime Implicants & Essential Prime Implicants. 2M2. With neat logic diagram, truth table & output expressions explain a) Binary Half Subtractor 2Mb) Binary Full Adder **4M** Part B 3. Simplify the Boolean function using K-MAP  $f(a,b,c,d) = \sum m(0,1,3,5,8,9,12,14,15) + \sum d(2,11,13)$ **5M 4.** Explain the steps involved in Quine McCluskey method to find Essential. **5M** Prime Implicants. Also explain how step-1 is carried out to find Prime Implicants. 5. Simplify the Boolean function using K-MAP and find the output expression for POS(f'). f(a,b,c,d,e) = $\sum$ m (0,2,4,5,9,10,14,16,24) +  $\sum$ d (19,21,30) **7M** Part C

**6.** Simplify the Boolean Function using Quine McCluskey method.

F(a,b,c,d,e) =

$\Sigma$ m(0,1,2,5,6,7,8,12,15,16,21,23,24,26,29,30,31)