| ROLL NO |  |  |  |  |  |  |  |

|---------|--|--|--|--|--|--|--|

|         |  |  |  |  |  |  |  |

# PRESIDENCY UNIVERSITY BENGALURU

## **SCHOOL OF ENGINEERING**

## **MAKEUP EXAMINATION – JAN 2023**

| Course Code: ECE215                                                       | <b>Date</b> : 27-JAN-2023                                                          |

|---------------------------------------------------------------------------|------------------------------------------------------------------------------------|

|                                                                           | <b>Time</b> : 01:00 PM TO 04:00 PM                                                 |

| Course Name: VLSI DESIGN                                                  | Max Marks: 100                                                                     |

| Program : B.Tech                                                          | Weightage: 50%                                                                     |

| Instructions:                                                             |                                                                                    |

| (i) Read the question carefully a                                         | nd answer all the questions                                                        |

| Part A[Mem                                                                | ory Recall Questions]                                                              |

| Answer all the Questions. Each Question                                   | carries TWO marks (20Qx2M=40M)                                                     |

| 1.CMOS inverter has distinct regions                                      | ons of operation which can be determined by plotting CMOS (C.O.2)[Knowledge Level] |

| a) three                                                                  |                                                                                    |

| b) four                                                                   |                                                                                    |

| c) two<br>d) five                                                         |                                                                                    |

| ,                                                                         | petween source and drain, then it is in region                                     |

| 2.11 IT translator conducte and had large voltage i                       |                                                                                    |

| a) linear                                                                 | (C.O.2)[Knowledge Level]                                                           |

| <ul><li>a) linear</li><li>b) saturation</li></ul>                         |                                                                                    |

| c) non saturation                                                         |                                                                                    |

| d) cut-off                                                                |                                                                                    |

| 3.If both the transistors are in saturation, then th between Vdd and Vss. | ey act asso that the equivalent circuit is two (C.O.2)[Knowledge Level]            |

| a) current source                                                         |                                                                                    |

| b) voltage source                                                         |                                                                                    |

| c) divider                                                                |                                                                                    |

| d) buffer                                                                 |                                                                                    |

| 4.                   | If $\beta n = \beta p$ , then Vin = which implies that the changeover between etrically disposed about the point.                                                | logic levels is  (C.O.3)[Knowledge Level]              |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| a)<br>b)<br>c)       | etrically disposed about the point.  ) Vdd  ) Vss  ) 2Vdd  ) 0.5Vdd                                                                                              | ( <b>C.O.3)</b> [Knowledge Level]                      |

| 5.<br>and n-         | Mobility is affected by the and thus also depends on Vgs a device are inherently unequal.                                                                        | nd the mobility of p-device (C.O.2)[Knowledge Level]   |

| b)                   | Transverse electric field Vg Vdd Channel length                                                                                                                  |                                                        |

| 6.<br>MOSF           | Under Gradual Channel Approximation (GCA), the depletion region in the FET on application of a drain bias                                                        | bulk of the long channel C.O.2)[Knowledge Level]       |

| b.<br>c.             | Reduces as we move towards the drain end Increases as we move towards the drain end Remains constant Has no relationship                                         |                                                        |

| 7.<br>should         | In order to remove the body effect, the substrate of an n-channel enhance be (C.                                                                                 | ment mode MOSFET  O.2)[Knowledge Level]                |

| b.<br>c.             | Connected to the most positive bias Connected to the most negative bias Grounded Floating                                                                        |                                                        |

|                      | a bulk MOSFET with aspect ratio of W/L and a depletion width of XD the arco-drain overlap capacitance (Cgd) is (C.                                               | nalytical expression for <b>O.3)</b> [Knowledge Level] |

| b.<br>c.             | Cgd = 2CoxWXD  Cgd = CoxXDW/2  Cgd = 2CoxXDWL  Cgd = CoxXDWL                                                                                                     |                                                        |

|                      | tatic CMOS Inverter is powered by a supply voltage of VDD. Assuming the process rks are equal and symmetric, which of the following statement are true <b>(C</b> | •                                                      |

| a.<br>b.<br>c.<br>d. | The switching threshold is VDD/2 The switching threshold is 2VDD The switching threshold is VDD The switching threshold is VDD/4                                 |                                                        |

| 40 5         |                                                                                                                                                                                      | <b>.</b>                                       |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| 10. F        | or a static CMOS, the output is high, then the state of the NMOS and PMOS                                                                                                            | s are as follows                               |

| b            | <ul> <li>NMOS on and PMOS non-linear</li> <li>NMOS off and PMOS linear</li> <li>NMOS off and PMOS non-linear</li> <li>NMOS on and PMOS linear</li> </ul>                             | (C.O.3)[Knowledge Level]                       |

| 11. lı<br>be | n order to remove the body effect, the substrate of an n-channel enhanceme                                                                                                           | nt mode MOSFET should (C.O.2)[Knowledge Level] |

| b<br>c       | <ul><li>Connected to the most positive bias</li><li>Connected to the most negative bias</li><li>Grounded</li><li>Floating</li></ul>                                                  |                                                |

|              | A bulk n-channel enhancement mode MOSFET is biased in the saturation /DS> VGS – Vth. Vth is the threshold voltage. Taking into consideration Chaffective channel length is given as: | •                                              |

| b            | . L'=L-ΔL<br>. L'=L-2L<br>. L'=L- μL<br>. L'=L- ÜL                                                                                                                                   |                                                |

| 13. lı       | n constant field model, the scaling factor of switching energy per gate would                                                                                                        | be                                             |

|              |                                                                                                                                                                                      | (C.O.2)[Knowledge Level]                       |

| b<br>c       | <ul> <li>1/βα^2</li> <li>1/ α^3</li> <li>1/ α^2</li> <li>All of the mentioned</li> </ul>                                                                                             |                                                |

| 14.          | CMOS inverter has output impedence                                                                                                                                                   | (C.O.3)[Knowledge Level]                       |

| b            |                                                                                                                                                                                      |                                                |

| 15. F        | eduction in power dissipation can be brought by                                                                                                                                      | (C.O.3)[Knowledge Level]                       |

| a<br>b<br>c  | Decreasing transistor area Increasing transistor feature size                                                                                                                        |                                                |

| <ul><li>a) a single diode</li><li>b) two diodes</li><li>c) three diodes</li><li>d) four diodes</li></ul>                                                                                                                             |                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| 18. The condition for non saturated region is In non saturation reg source. Varying Vds will provide a significant change in drain current.                                                                                          | _                                          |

| <ul> <li>a) Vds = Vgs - Vt</li> <li>b) Vgs lesser than Vt</li> <li>c) Vds lesser than Vgs - Vt</li> <li>d) Vds greater than Vgs - Vt</li> </ul>                                                                                      |                                            |

| 19. In enhancement mode the device is in non conducting mode, and its con                                                                                                                                                            | dition is                                  |

| a) Vds lesser than Vgs<br>b) Vgs lesser than Vds                                                                                                                                                                                     | (C.O.2)[Knowledge Level]                   |

| c) Vgs = Vds = 0<br>d) Vgs = Vds = Vs = 0                                                                                                                                                                                            |                                            |

|                                                                                                                                                                                                                                      | (C.O.2)[Knowledge Level]                   |

| d) $Vgs = Vds = Vs = 0$                                                                                                                                                                                                              | (C.O.2)[Knowledge Level]                   |

| d) Vgs = Vds = Vs = 0  20. MOS transistor structure is  a) symmetrical b) non symmetrical c) semi symmetrical                                                                                                                        |                                            |

| d) Vgs = Vds = Vs = 0  20. MOS transistor structure is  a) symmetrical b) non symmetrical c) semi symmetrical d) pseudo symmetrical                                                                                                  |                                            |

| d) Vgs = Vds = Vs = 0  20. MOS transistor structure is  a) symmetrical b) non symmetrical c) semi symmetrical d) pseudo symmetrical  Part B [Thought Provoking Question                                                              | s]                                         |

| d) Vgs = Vds = Vs = 0  20. MOS transistor structure is  a) symmetrical b) non symmetrical c) semi symmetrical d) pseudo symmetrical  Part B [Thought Provoking Question  Answer both the Questions. Each Question carries TEN marks. | s] (3Qx10M=30M) (C.O.NO.1) [Comprehension] |

(C.O.3)[Knowledge Level]

16. Pmos used as a pull up network because of

### Part C [Problem Solving Questions]

#### Answer the Question. The Question carries FIFTEEN marks.

(3Qx15M=30M)

1.Explain the steps of N-MOS fabrication with neat diagram.

(C.O.NO.2) [Comprehension]

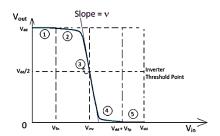

- 2. A typical CMOS inverter has the voltage transfer characteristics VTC curve as shown the figure

- i. Determine the Gain in region 2 and region 4

- ii. At region1, both the Pmos and Nmos transistors are operated in

- iii. For calculating Switching threshold of an CMOS inverter the region of P and N transistors are (C.O.NO.3) [Comprehension]

Plot of output voltage vs input voltage