| Roll No |  |  |  |  |  |  |

|---------|--|--|--|--|--|--|

Date: 24/01/2023

## PRESIDENCY UNIVERSITY BENGALURU

## SCHOOL OF ENGINEERING

#### MAKE UP EXAMINATION – JAN 2023

|                             | Dute: 21/01/2020                 |  |  |  |

|-----------------------------|----------------------------------|--|--|--|

| Course Code: ECE 323        | <b>Time:</b> 9:30 AM to 12:30 PM |  |  |  |

| Course Name: VLSI CAD Tools | <b>Max Marks</b> : 100           |  |  |  |

| Program : B. Tech           | Weightage: 50%                   |  |  |  |

|                             |                                  |  |  |  |

#### Instructions:

(i) Read the all questions carefully and answer accordingly.

(ii) Use of scientific (non – programmable ) calculators is permitted

### Part A [Memory Recall Questions]

### Answer all the Questions. Each question carries TWO marks.

(10Q x 2M = 20M)

(C.O.No.2) [Knowledge]

1. The VLSI design flow consists of three domains namely Physical, Behavioral and Structural.

Outline the Y-chart design methodology.

**2.** The problems in the optimization of combinational circuit are referred as Decision problem. Depict the classification of all decision problems in circuit design (C.O.No.2) [Knowledge]

3. Layout is the representation of CMOS circuits for real time implementation. Define layout compaction? (C.O.No.2) [Knowledge]

**4.** The algorithmic graph theory is utilized for the complex computation problems. Define clique with example (C.O.No.1) [Knowledge]

**5.** Integrated Circuits Layout design is based on Design rules that are expressed in terms of minimum distance rules. Classify the types of minimum distance rules used in IC fabrication.

(C.O.No.3) [Knowledge]

**6.** The wire length estimation is used to evaluate the quality of placement. List the common metrics in wire length estimation. (C.O.No.3) [Knowledge]

**7.** In VLSI design, the circuit designs are represented using the mathematical models. Define Formal verification and explain the disadvantages. (C.O.No.1) [Knowledge]

8. In VLSI design flow, the physical design steps are the core of IC fabrication. In physical design, the placement is the process of finding a suitable physical location for each cell in the block. To accomplish the optimized placement, describe the goals of Placement? (C.O.No.3) [Knowledge]

9. The routing consists of some issues in terminal interconnections. List the problems in local (C.O.No.4) [Knowledge]

**10.** In VLSI design, routing is important to interconnect different blocks. Classify the types of routing. (C.O.No.4) [Comprehension]

### Answer all the Questions. Each question carries EIGHT marks.

$(4Q \times 8M = 32M)$

**11.** Placement is integral part of the physical design of the VLSI Design flow. There are two types of Placement algorithms in real time. Demonstrate the importance of Constructive Placement and its types with suitable examples (C.O.No.3) [Application]

**12.** The physical realization of CMOS circuits is developed using the layout and its rules. Making use of the design rules, depict the CMOS inverter Layout and its CMOS circuit diagram.

(C.O.No.3) [Application]

**13.** Channel Routing consists of interconnection issues in real time. Differentiate between the Vertical Constraint Graph and Horizontal Constraint Graph in Channel routing.

(C.O.No.4) [Analyze]

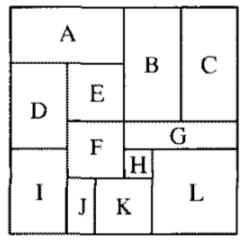

**14.** Floorplan determines the size, shape, and locations of modules in a chip and as such it estimates the total chip area, the interconnects, and, delay. Develop the Slicing Tree for the Floor plan shown in Fig.1.

Fig.1

(C.O.No.3) [Application]

# Part C [Problem Solving Questions]

### Answer all the Questions. Each question carries TWELVE marks. (4Q x 12M = 48M)

15. The layout is the physical realization of circuits that consists of CMOS transistors. The layout follows certain rules in the design of circuits. Making use of the design rules, depict the CMOS NAND stick diagram along with the CMOS circuit diagram. (C.O.No. 2) [Application]

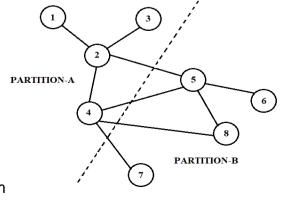

16. There are 8 blocks as shown in Fig.2. The blocks are to be effectively placement using the constructive algorithms. Evaluate the optimized partition for the following diagram using the

Kernighan-Lin Algorithm Fig.2

(C.O.No. 3) [Application]

**17.** In routing, the connection between two terminals is complex when there exist a block between terminal. Build the connection between two terminals S and T as shown in Fig 3 by using Maze routing algorithm.

(C.O.No. 4) [Application]

**18.** Algorithmic Graph theory is used to represent the complex computations in digital design without having to deal with specific hardware. Develop the Breadth First search algorithm using suitable example.

(C.O.No. 1) [Application]