| PRESIDENCY UNIVERSITY<br>BENGALURU       |                            |  |  |

|------------------------------------------|----------------------------|--|--|

| SCHOOL OF ENGINEERING                    |                            |  |  |

| END TERM EXAMINATION August-2024         |                            |  |  |

| Even Semester: M.Tech 2023 - 24          | Date: 13 /08 /2024         |  |  |

| Course Code: ECE5006                     | Time: 09:30 AM to 12:30 PM |  |  |

| Course Name: Hardware Software Co-design | Max Marks: 100             |  |  |

| Program & Sem: M.Tech ESV                | Weightage: 50%             |  |  |

Roll No

#### Instructions:

(i) Read the all questions carefully and answer accordingly. All parts are compulsory.

(ii) Do not write any information on the question paper other than Roll Number.

#### Part A [Memory Recall Questions]

## Answer any 3 Questions. Each question carries 5 marks. (3Qx 5M= 15M)

1. A Kahn Process network (KPN) consist of monotonic processes. Describe how KPN is determinate. (CO 1) [Knowledge]

2. System synthesis includes allocation, binding and scheduling. Explain with diagram the process of system synthesis. (CO 2) [Knowledge]

3. Mapping relates application and architecture specifications. Describe specification graph. (CO 3) [Knowledge]

4. In multi-objective optimization explain the black box optimization. (CO 4) [Knowledge]

5. The decision space using the objective function is denoted by objective space. Explain Pareto optimal set. (CO 4) [Knowledge]

### Part B [Thought Provoking Questions]

(4Qx10M=40M)

### Answer any 4 Questions. Each question carries 10 marks.

6. The Integer Programming (IP) model consist of an objective function C involving linear expressions of integer variables from a set X is given below. Determine the optimal solution for the IP. (CO 2) [Comprehension]

Objective function: C = 3 x1 + 5 x2 + 7 x3Subject to:  $x1 + x2 + x3 \ge 2$  $x1, x2, x3 \in \{0, 1\}$

7. The system is represented by structural and behavioral objects. Represent the behavioral properties of the following algorithm in control flow graph (CFG) (CO 2) [Comprehension]

|    | Compare_GT_EQ_I     | LT {           |  |

|----|---------------------|----------------|--|

| 1  | read (a, b);        |                |  |

| 2  | done = FAL          | SE;            |  |

| 3  | repeat {            |                |  |

| 4  | if(a>b) {           |                |  |

| 5  |                     | GT = a;        |  |

| 6  |                     | LT = b;}       |  |

| 7  | els                 | elseif (b>a) { |  |

| 8  |                     | GT = b;        |  |

| 9  |                     | LT = a;}       |  |

| 10 | else {              |                |  |

| 11 |                     | EQ = a;        |  |

| 12 |                     | done = TRUE;}  |  |

| 13 | } until don         | e;             |  |

| 14 | write (GT, EQ, LT); |                |  |

|    | }                   |                |  |

8. The state set by traversing the tree is represented using the following equation.

$\begin{aligned} & \mathsf{Q}_{\mathsf{A}} = (\mathsf{Q}_{\mathsf{C}} \cup \mathsf{Q}_{\mathsf{D}}) \times (\mathsf{Q}_{\mathsf{M}} \cup ((\mathsf{Q}_{\mathsf{I}} \cup \mathsf{Q}_{\mathsf{K}}) \times \mathsf{Q}_{\mathsf{L}})) \\ & \mathsf{Q}_{\mathsf{A}} = \mathsf{Q}_{\mathsf{B}} \times \mathsf{Q}_{\mathsf{E}} \\ & \mathsf{Q}_{\mathsf{B}} = \mathsf{Q}_{\mathsf{C}} \cup \mathsf{Q}_{\mathsf{D}} \\ & \mathsf{Q}_{\mathsf{B}} = \mathsf{Q}_{\mathsf{C}} \cup \mathsf{Q}_{\mathsf{D}} \\ & \mathsf{Q}_{\mathsf{F}} = \mathsf{Q}_{\mathsf{F}} \cup \mathsf{Q}_{\mathsf{M}} \\ & \mathsf{Q}_{\mathsf{F}} = \mathsf{Q}_{\mathsf{G}} \times \mathsf{Q}_{\mathsf{H}} \\ & \mathsf{Q}_{\mathsf{G}} = \mathsf{Q}_{\mathsf{I}} \cup \mathsf{Q}_{\mathsf{K}} \\ & \mathsf{Q}_{\mathsf{H}} = \mathsf{Q}_{\mathsf{L}} \end{aligned}$

Draw the tree representation for the state set.

(CO 1) [Comprehension]

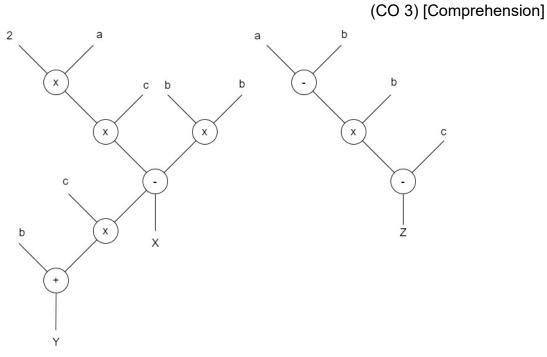

9. Mapping often require only the process network structure and its abstract properties. Derive the equation from the abstraction in data flow graph (DFG) shown in Fig 1.

Fig 1

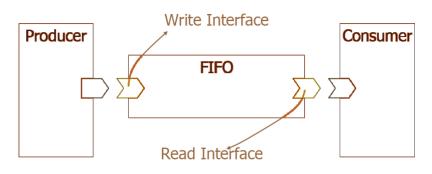

10. A simple producer-consumer application is illustrated in Fig 2. Write program module of simple FIFO read and write interfaces, and FIFO implementation (CO 4) [Comprehension]

Fig 2

11. The optimization analysis cycle consist of a decision vector X and objective vector f(X). Explain with diagram the optimization analysis cycle. (CO 4) [Comprehension]

# Part C [Problem Solving Questions]Answer any 3 Questions. Each question carries 15 marks.(3Qx15M=45M)

12. A system modeled by an SDF graph has four processes named 'A', 'B', 'C', and 'D', and has the following topology matrix: (CO 1) [Apply]

$$\begin{bmatrix} 4 & -3 & 0 & 0 \\ -2 & 0 & 3 & 0 \\ 0 & 1 & -2 & 0 \\ 1 & 0 & 0 & -3 \\ 0 & 0 & -1 & 2 \end{bmatrix}$$

a. Draw the SDF graph and attach labels to the heads and tails of edges that represent the number of tokens consumed and produced at each firing of the corresponding process.b. Determine the relative execution rates and periodic schedule.

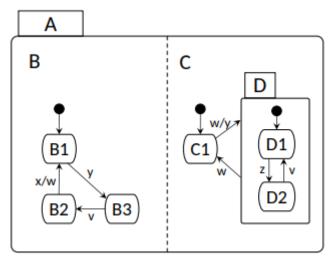

13. Consider the state chart shown in Fig 3.

(CO 2) [Apply]

- a. Consider the following sequence of external events: x, w, y, y, z, v, x. Determine the sequence of states, the automaton in Fig. passes through, starting from the initial state.

- b. Draw a finite state machine (FSM) which is equivalent to the StateChart.

- 14. Consider the digital circuit shown in Fig 4

(CO 3) [Apply]

Fig 4

- a. Tabulate the cost matrix c(x,y) that assess the communication cost from node x to y.

- b. Partition the circuit using the KL algorithm and find the best solution.

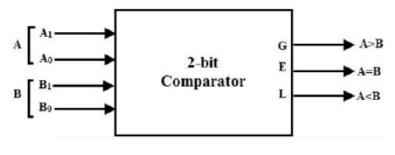

15. A comparator is to be designed to compare greater than, equal and less than. Implement in Verilog/VHDL code a 2-bit comparator shown in Fig 5. with Test bench to verify the design. The entity has two 2-bit inputs and three 1-bit outputs. (CO 4) [Apply]

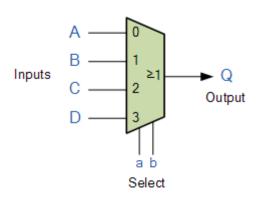

16. Implement in Verilog/VHDL code a 4:1 MUX shown in Fig 6. with Test bench to verify the design. The entity has four 1-bit inputs and one 2-bit select input. The output is a 1-bit wire. (CO 4) [Apply]